CRYSTALWALLET

BITCOIN-ONLY · AIR-GAPPED · OPEN SOURCE

Die nächste Generation sicherer Hardware-Wallets. Entwickelt in Deutschland von Crystalwallet UG — kompromisslose Sicherheit durch vollständige Netzwerkisolierung, kryptographische Hardware-Chips und transparenten Open-Source-Code.

UNSERE PROJEKTE

Zwei bahnbrechende Projekte. Eine Mission.

🔐

Crystalwallet V.0.01

HARDWARE WALLET

Bitcoin-only, vollständig air-gapped Hardware Wallet. STM32U5G9 ARM Cortex-M33 mit TrustZone, zwei verschiedene Secure Elements (TROPIC01 + ATECC608A), 4″ Display, QR-Scanner für Offline-Transaktionen. 6-Layer PCB, entwickelt in Deutschland.

⚛️

SecureQ-Core

POST-QUANTUM CHIP IP

Post-Quantum Cryptography ASIC IP-Core. Quantenresistente Kryptografie-Hardware für die nächste Generation sicherer Systeme. CRYSTALS-Kyber und Dilithium Algorithmen, optimiert für minimalen Stromverbrauch und maximale Sicherheit.

HARDWARE SPECS

Kompromisslose Sicherheitsarchitektur

⚡

STM32U5G9

ARM Cortex-M33 mit TrustZone, UFBGA-144, Ultra-Low-Power MCU mit Hardware-Kryptobeschleuniger

🛡️

TROPIC01

Tropic Square Open-Source Secure Element, SPI-Interface, QFN-32, transparente Sicherheit

🔒

ATECC608A

Microchip Secure Element, I2C mit galvanischer Isolation (ADUM1250), ECDSA/ECDH

📷

QR Air-Gap

GM67 Scanner, Offline-Transaktionen via QR-Code, kein USB-Daten

SICHERHEITSARCHITEKTUR

Warum air-gapped?

🔌 Kein USB-Daten

USB-C nur für Strom — Datenleitungen physisch nicht geroutet. SMBJ5.0A TVS-Schutz am VBUS. Remote-Angriffe sind hardwareseitig unmöglich.

🔒 Zwei verschiedene SEs

TROPIC01 (Open-Source, SPI) + ATECC608A (I2C mit ADUM1250 galvanischer Isolation). Zwei unabhängige Sicherheitschips verschiedener Hersteller.

📡 6-Layer PCB

Dedizierte Ground- und Power-Planes für EMI-Abschirmung. Signalisolation zwischen sensitiven Bereichen. Ferrite-Bead-Filterung.

🛡️ TrustZone MCU

STM32U5G9 mit ARM TrustZone: Hardware-Trennung zwischen sicherer und nicht-sicherer Firmware-Ausführung. Kein JTAG nach außen.

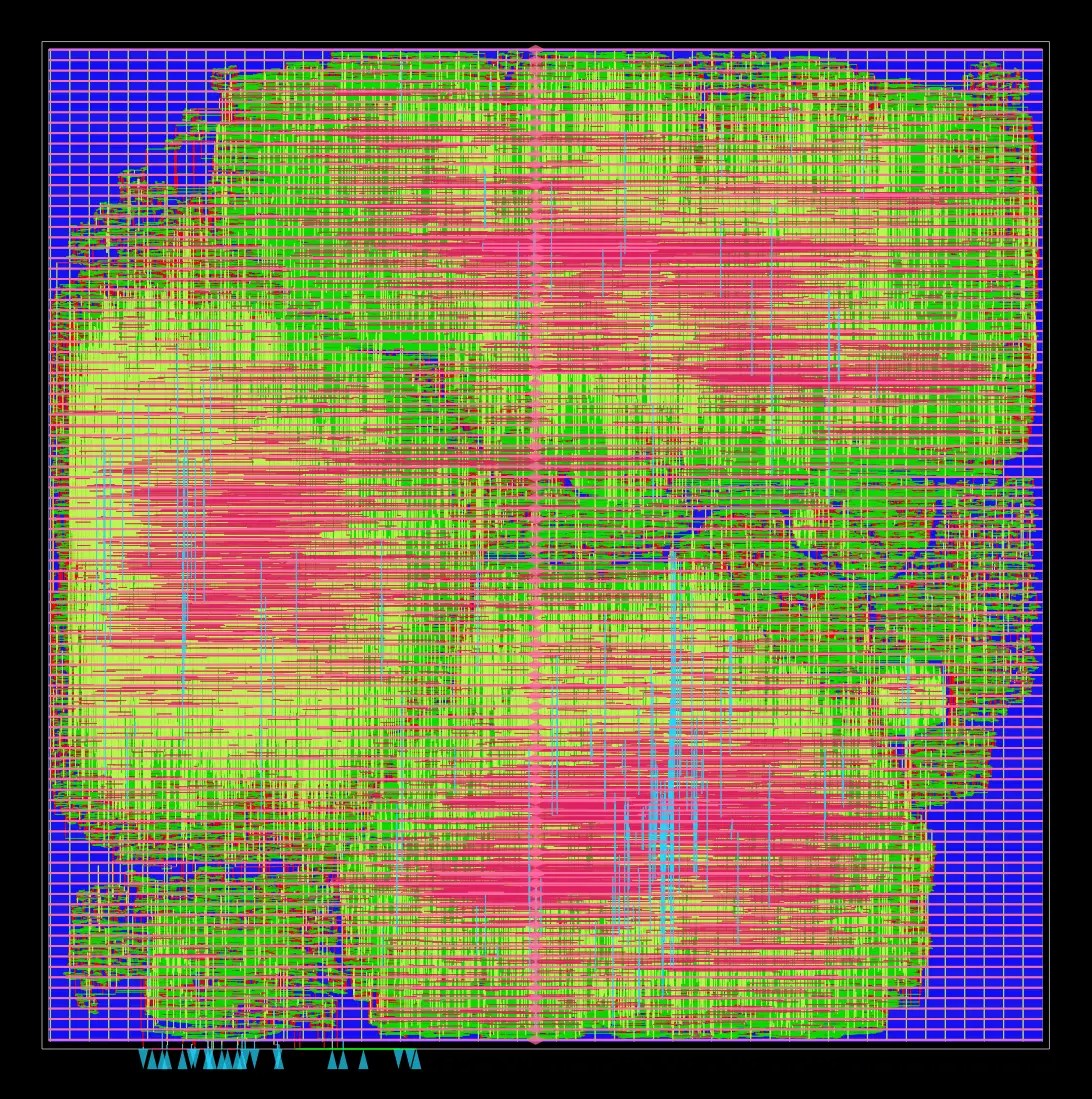

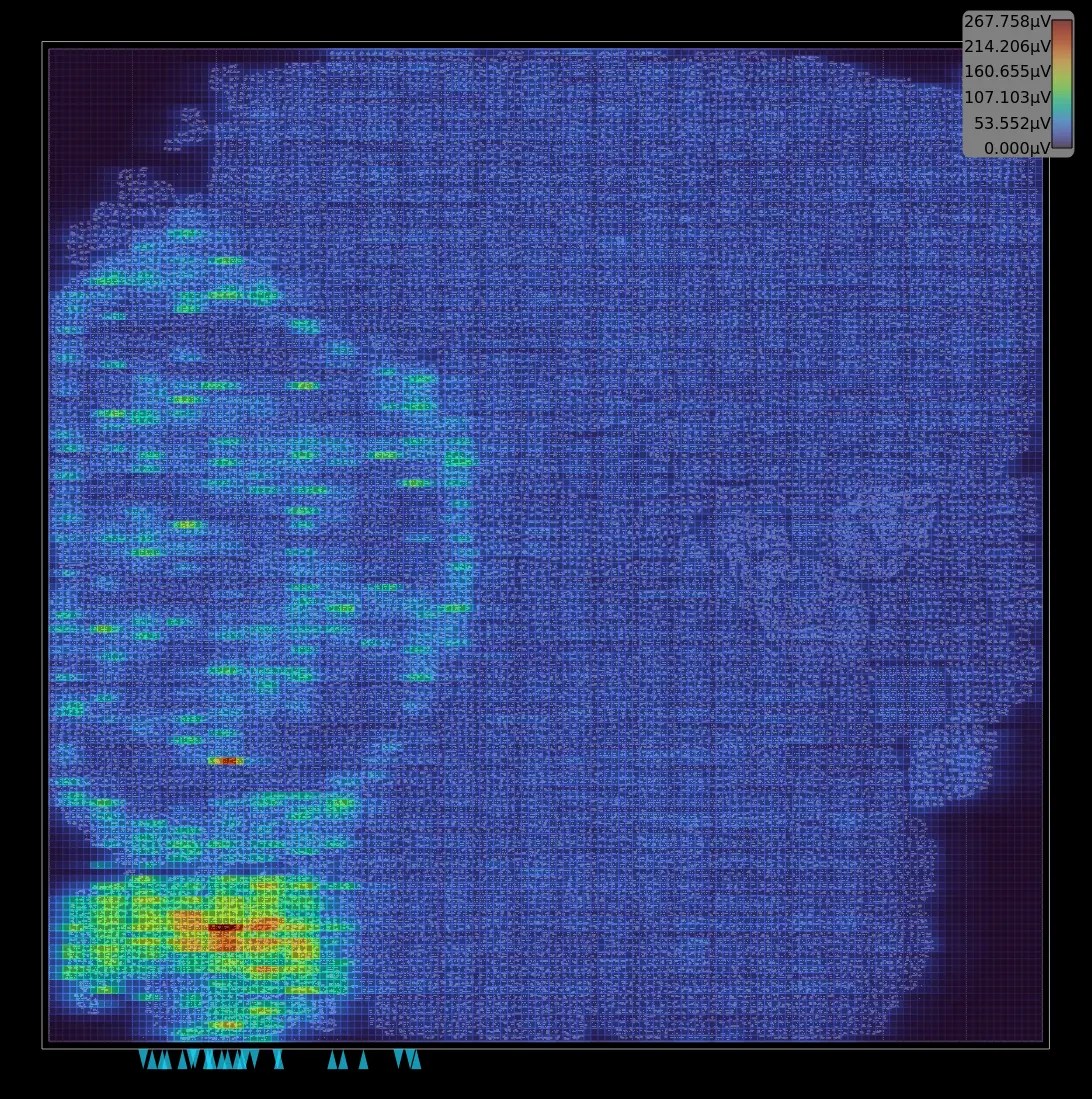

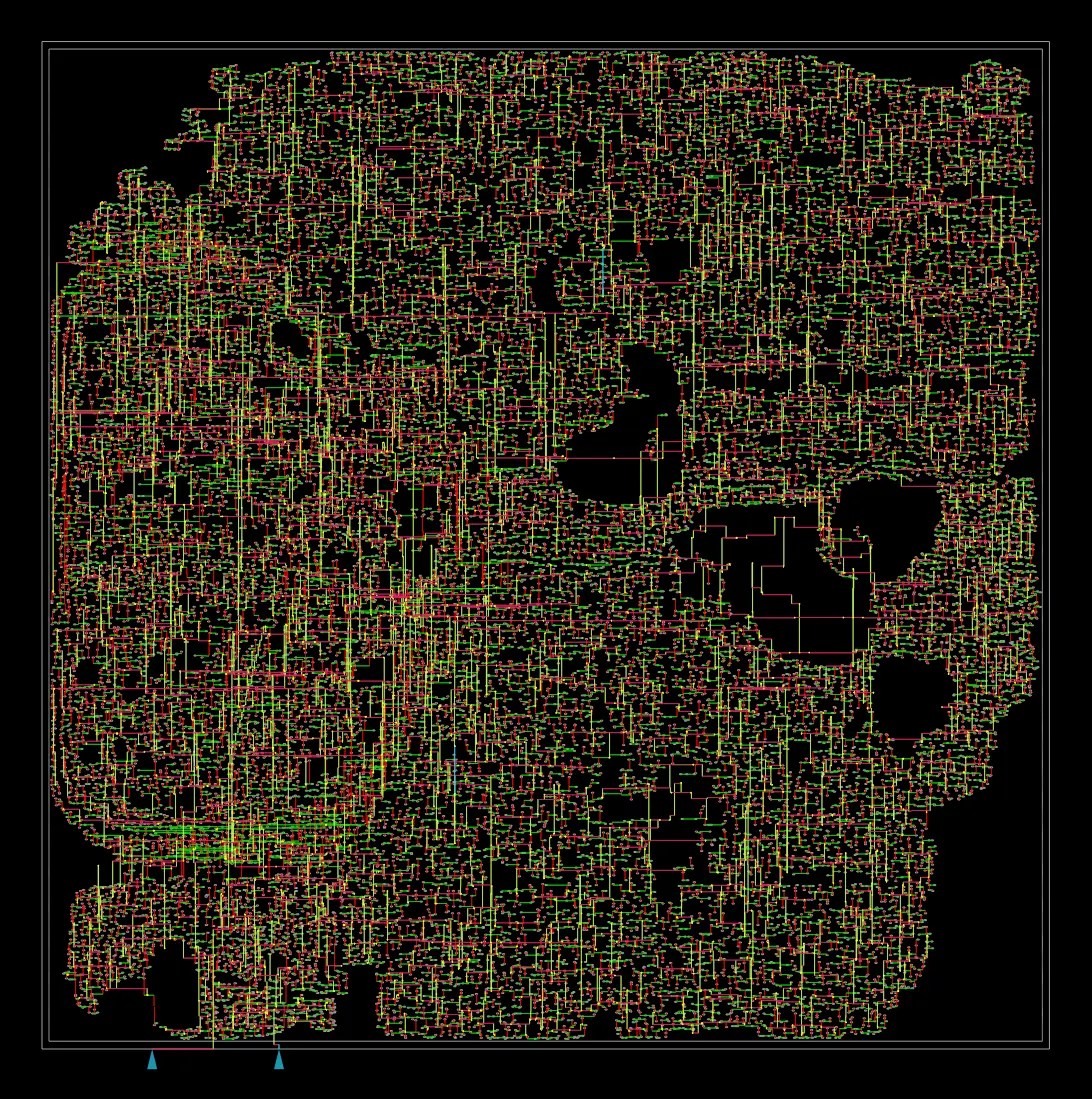

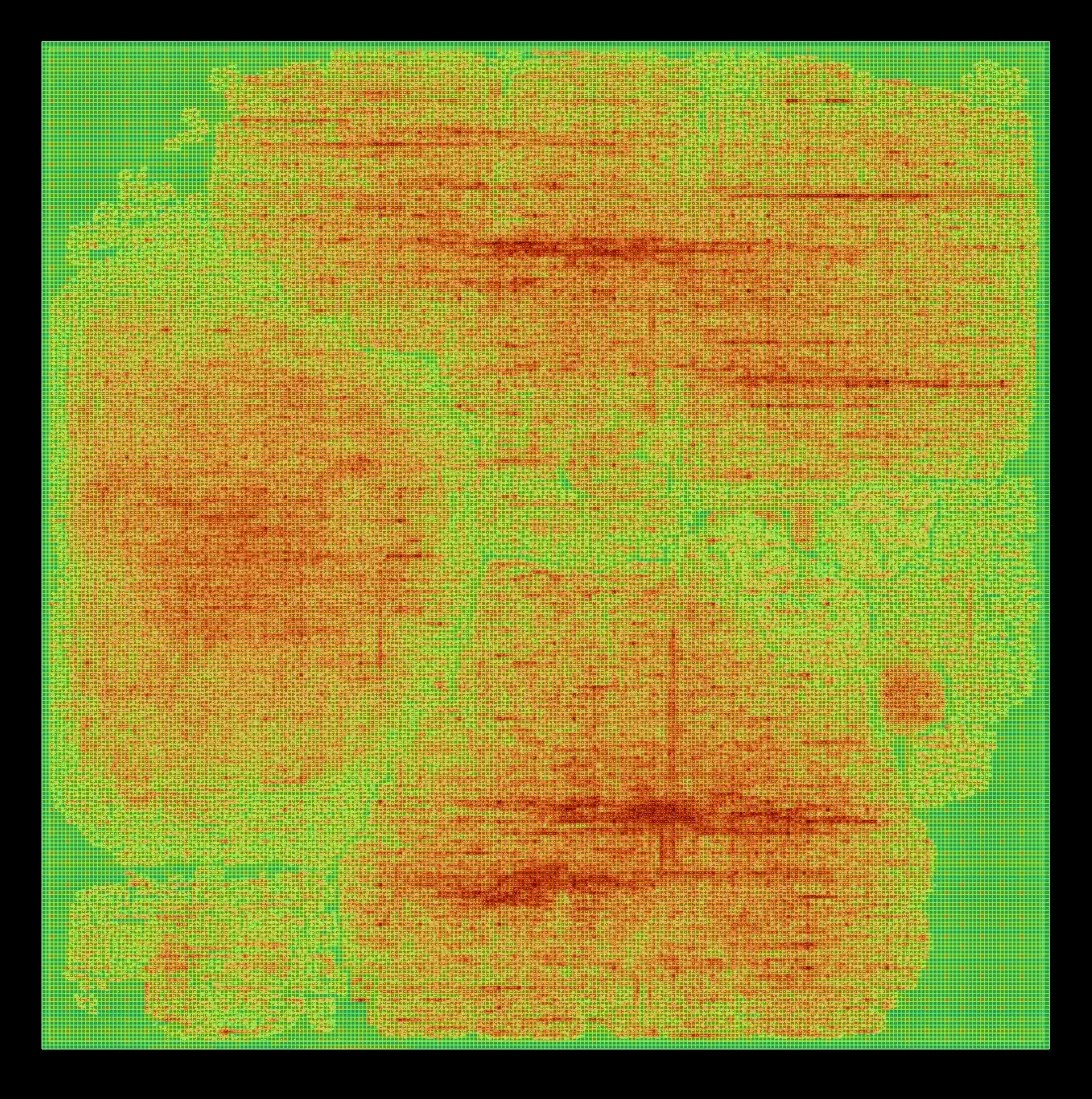

PQC CHIP DESIGN

SecureQ-Core — ASIC Layout

Post-Quantum Cryptography ASIC — synthetisiert und geroutet mit OpenROAD auf NanGate45 PDK. 176K Instances, 113 MHz, 0 Setup-Violations.

NEWSLETTER

Bleib informiert

Erhalte Updates zu Entwicklung, Roadmap, technischen Details und Early Access Möglichkeiten.